热线电话:0755-23712116

邮箱:contact@shuangyi-tech.com

地址:深圳市宝安区沙井街道后亭茅洲山工业园工业大厦全至科技创新园科创大厦2层2A

半导体知识:集成电路是怎么制造出来的?

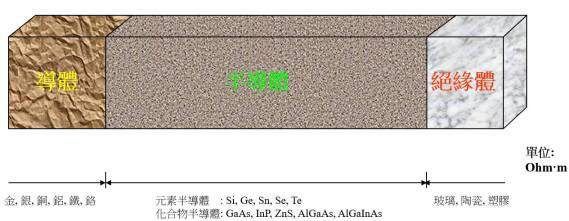

半导体是导电性介于导体(金属)与绝缘体(陶瓷、石头)之间的物质,包括硅、锗。

利用半导体制作电子组件的目的在于:不像导体绝对导电、绝缘体完全不导电;藉由注入杂质,可以精准地调整半导体的导电性。由于硅拥有较大的能隙、可以有较大杂质掺杂范围,所以可以被利用来制作重要的半导体电子组件晶体管 (Transistor)。

由于发明了晶体管,这个年代成为人类科技文明进步最快的年代,电子技术与计算机工业才开始了长足的发展,堪称二十世纪最伟大的发明之一。

发明晶体管的萧克利 (Shockley)、巴丁 (Bardeen) 与布拉顿 (Brattain) 三位物理学家在1956年共同荣获诺贝尔奖。

1956年,萧克利在旧金山南方成立萧克利半导体实验室 (Shockley Semiconductor Lab),带动美国硅谷 (Silicon Valley) 的蓬勃发展,硅谷一名称系由半导体原料硅而来。

讲到硅谷的发展成因与历史,绝对不能不提萧克利半导体实验室的影响。一个天才的创业会引来众多天才的投奔,因此当时一堆优秀人才趋之若鹜地跑到萧克利的实验室来;但后来因萧克利暴躁又疑神疑鬼的性格,又纷纷辞职离去,被萧克利怒称为「八叛徒」(The Traitorous Eight)。

八位叛徒中,包括了诺伊斯 (Noyce)、摩尔 (Moore,就是摩尔定律的那个摩尔!) 等人,他们随后成立了快捷半导体 (Fairchild Semiconductor),成为了第一家将硅晶体管商业化的公司。

这家公司最重要不是它的产品、而是影响力——快捷可说是硅谷人才的摇篮,创始人和员工出来开的公司和投资的公司在湾区超过 130家上市企业,里面包括了 Intel、AMD 等公司,市值达 21 万亿美元。对硅谷乃至当今时代的科技发展都有着不可或缺的影响和作用。

好啦此为后话不提,让我们回来看看硅谷发展一切的源头——晶体管到底是什么。

晶体管的主要功能有两个:「放大信号」与「开关」。

晶体管就像是数字信号的「收音机」──收音机的原理是将微弱的信号放大、用喇叭发声出来,晶体管能将信号的电流放大;而数字信号是由0与1组成,1代表着电流「开」、0代表着电流「关」,晶体管以每秒超过 1千亿次的开关来运作,让电流以特定方式通过。

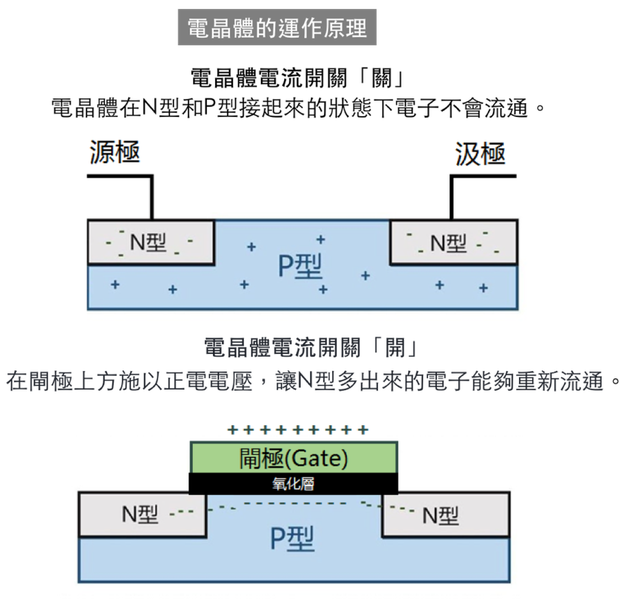

这边让我们来简单谈谈晶体管的运作原理。

晶体管由硅组成,而硅是 4 颗电子。在硅半导体中加入元素磷,具有 5 颗电子、比硅多一颗电子(-)变成 N 型晶体管 (Negative)。

另外加入元素硼,具有 3 颗电子、 比硅少一颗电子(-)变成 P 型晶体管 (Positive) 。晶体管两端可以通电,称为「源极」和「汲极」。

由于P型和N型分别多了电子和少了电子,所以晶体管在 N 型和 P 型接起来的状态下电子不会流通,此时电流开关为「关」。

为了达到开关的效果,我们使用第三个电极「闸极」(Gate) 取代机械按钮开关;闸极间以氧化层和半导体隔绝。若我们在闸极上方施以正电电压,让 N 型多出来的电子能够重新流通、并从源极流到汲极,此时电流开关为「开」。

上述即为半导体组件晶体管如何藉由加入杂质(磷、硼)来控制导电性、进而控制电流开关的原理。

但是这数亿个晶体管在哪里呢?你可能正在心想:「我手机有大到能放进数亿个晶体管?」

答案是:晶体管是纳米等级,比人体细胞还要小。三星以及台积电在先进半导体制程的 14 纳米与 16 纳米之争,14 纳米指的就是晶体管电流通道的宽度。宽度越窄、耗电量越低;然而原子的大小约为 0.1 纳米,14 纳米的通道仅能供一百多颗原子通过。故制作过程中只要有一颗原子缺陷、或者出现一丝杂质,就会影响产品的良率。

对于半导体大厂而言,制程是技术,但良率才是其中的关键Know-how。一般能将良率维持在八成左右已经是非常困难的事情了,台积电与联电的制程良率可以达到九成五以上,可见台湾晶圆代工的技术水平。

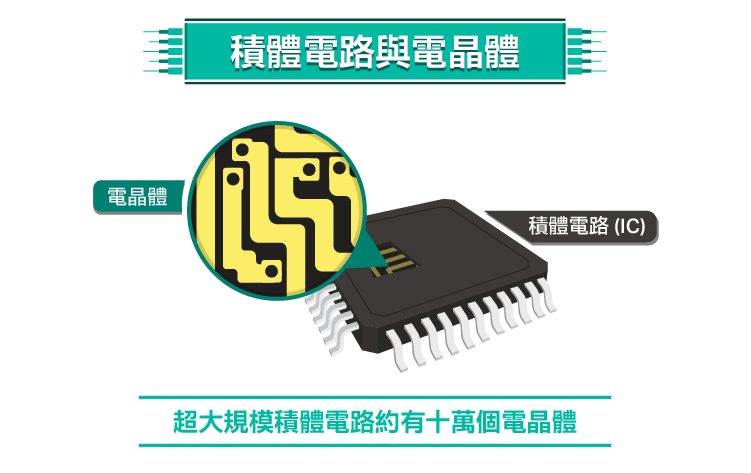

事实上,这数亿个晶体管,全部都塞在一个长宽约半公分、指甲大小的芯片上。这片芯片包含晶体管等电子组件,就叫做「集成电路」(Integrated Circuit, IC),俗称IC。

所谓的大规模集成电路 (LSI, Large Scale Integration) 代表的不是这个电路板很大,而是上面约一万个晶体管;超大规模集成电路 (VLSI, Very Large Scale Integration) 则约有十万个晶体管。

在集成电路出现之前,工业界必须各自生产晶体管、二极管、电阻、电容等电子组件,再把所有组件连接起来做成电路,不但复杂又耗时费工。故若能直接依照设计图做出一整个电路板,将能更加精确、速度更快且成本更低。

德州仪器公司的基尔比 (Jack St. Clair Kilby) 是第一个想到要把组件放到芯片上集体化的发明人,在1958年他试验成功,开辟了一个崭新的计算机技术时代,甚至很多学者认为由集成电路所带来的数字革命是人类历史中最重要的事件。基尔比也因此于2000年获得诺贝尔物理奖。

集成电路的制作过程分为以下步骤。

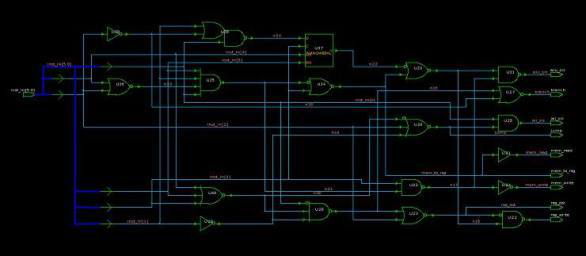

如同在盖房子之前,建筑设计师必须画出设计图,规划房间分布、使用材料;在制作半导体芯片时,工程师会画出电路图 (Circuit Diagram),规划一个芯片上应该要具备的功能 (包括算术逻辑、记忆功能、 浮点运算、 数据传输)、各个功能分布在芯片上的区域,与制作所需的电子组件。

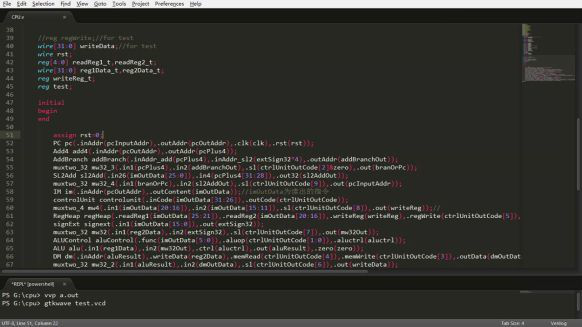

接下来,工程师会使用硬件描述语言 (HDL) 将电路图描写出来。

待确认无误后再将 HDL 程序代码放入电子设计自动化工具 (EDA tool),让计算机将程序代码转换成电路图。

设计师设计完房子后,就需要将电路设计图交由建筑工人将房子盖出来。盖房子需要地基,制作芯片也要,安置所有电子组件的基板就是「晶圆」(Wafer)。

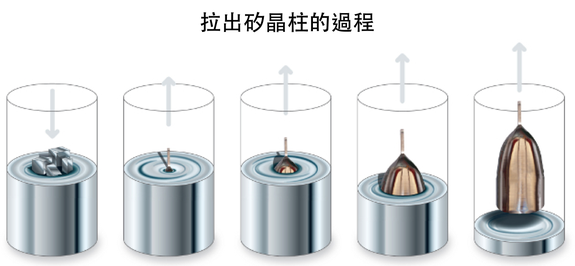

首先,晶圆制造厂会将硅纯化、溶解成液态,再从中拉出柱状的硅晶柱,上面有一格一格的硅晶格,后续可供晶体管安置上去。

也由于硅晶格的排列是安装电子组件的关键,「拉晶」的步骤非常重要──晶柱的制作过程就像是在做棉花糖一样,一边旋转一边成型,旋转拉起的速度以及温度的控制都会影响到晶柱的质量。

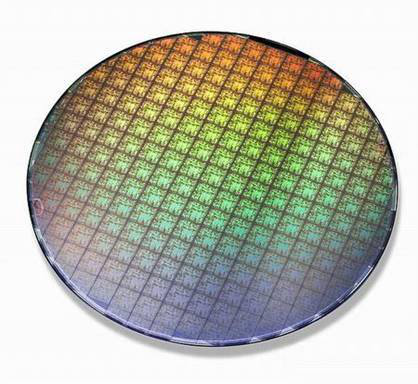

接下来,晶圆厂会用钻石刀像切火腿一般,将一整条的晶柱切成一片片的薄片,再经过抛光后,就变成了「晶圆」(Wafer),也就是芯片的基板;晶圆上面的晶格可供晶体管置入。

晶圆(Wafer)上面的晶格可供晶体管置入。

常听到的8吋、12吋晶圆厂,代表的就是硅晶柱切成薄片后的晶圆直径,而整块晶圆可以再被切成一片片的裸晶 (Die);裸晶经过封装后,才被称为芯片 (Chip)、或称 IC。

晶圆的尺寸,可以决定后续裁切制作出来的芯片有多少数量。

附注: AnySillicon网站上提供的计算器(Die Per Wafer Calculator)可供计算一块晶圆上能切出多少裸晶。

如直径8吋的晶圆片使用2.0微米的制程,可以切出588颗64M的DRAM (内存);至于12吋的晶圆,可以切出的成品又更多。

然而如先前所述,硅纯度、拉晶速度与温度控制都是晶柱质量的关键,越粗的硅晶柱越难拉出好质量,故尺寸越大、技术难度就越高,12吋晶圆厂也就比8吋晶圆厂的制程更先进。

另外,杂质对这些完美无缺的硅晶格构成很大的威胁(想想看:晶体管比人体细胞还小,稍有一丝杂质变足以毁坏整个硅晶格了),因此制造人员进入无尘室前,都必须事先清洗身体、穿戴防尘衣、全副武装采取预防措施。晶圆制造环境更比手术室干净十万倍。

晶圆会在无尘的状态下送到无尘室并分装到密封的容器中,进行随后的生产步骤。

我们在先前提到,集成电路 (IC) 跨时代的意义在于,工业界不用各自生产电子件再组建起来,可以一口气将电路板依据电路图生产出来。这是怎么做到的呢?

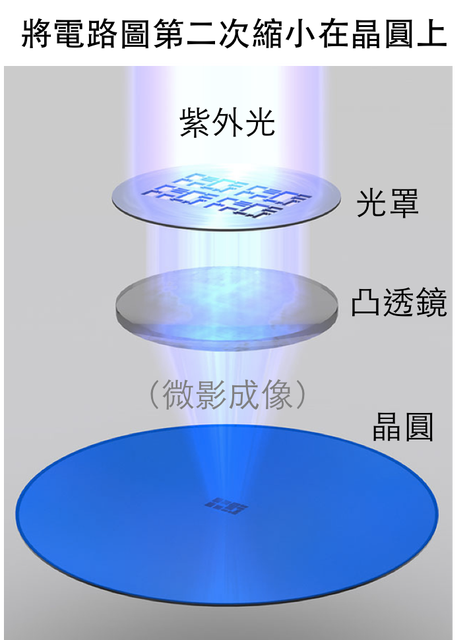

答案是:光学摄影技术。一大张的电路设计图,要缩小并压印到硅晶圆(基板),靠的就是光学原理。

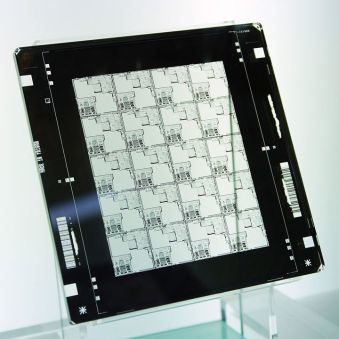

首先光罩厂会将IC设计图形第一次缩小,以电子束刻在石英片上,成为光罩。

光罩

由于电子束的宽度是1微米,所以光罩上依据设计图所刻出的半导体回路也是1微米宽。接下来光罩厂会将完成的光罩送进晶圆厂。

芯片制造,也就是将光罩上刻的设计图、第二度缩小至晶圆上。与底片洗出相片的原理一样,「光罩」就是照相底片、「晶圆」就是相片纸。

晶圆上面会事先涂上一层光阻 (相片感光材料),透过紫外光的照射与凸透镜聚光效果、会将光罩上的电路结构缩小并烙印在晶圆上,最后印在晶圆上的半导体回路会从光罩的 1 微米、变为 0.1 微米。阴影以外的部分会被紫外光破坏,随后能被冲洗液洗掉。

藉由光蚀刻与微影成像,晶圆厂成功将设计图转印到微小的晶圆基板上。如同底片质量会影响照片成像的好坏,光罩上图形的细致度是芯片质量的关键。

光刻制程结束后,工程师会在晶圆上继续加入离子。透过注入杂质到硅的结构中控制导电性,与一连串的物理过程,制造出晶体管。其过程相当复杂,甚至需要像两个足球场大的无尘室。

待晶圆上的晶体管、二极管等电子组件制作完成后,工程师会将铜倒入沟槽中形成精细的接线,将许多晶体管连结起来。在指甲大的空间里,数公里长的导线连接了数亿个晶体管,制作成大规模集成电路。至此,伟大的建筑就完成了。

晶圆完成后被送到封装厂,会切割成一片片的「裸晶」,如先前图所示。由于裸晶小而薄、非常容易刮伤,故封装厂会将裸晶安装在导线架上、在外面封装上绝缘的塑料体或陶瓷外壳,剪下来印上委托制造公司的标志。最后进行测试,进行芯片结构及功能的确认、将不良品挑出,一颗芯片就大功告成了!

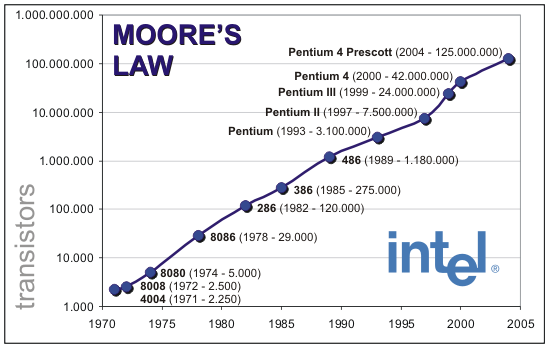

1960年代集成电路的发明,让许多的半导体组件可以一次放在一块芯片上。随着半导体的缩小,IC上可容纳的晶体管数目,约每隔两年便会增加一倍、性能每18个月能提升一倍 。

从1960年代不到10个,1980年代增加到10万个、1990年代增加到1000万个。这个现象由英特尔的名誉董事长摩尔所提出,称为摩尔定律 (Moore’s Law)。如今,集成电路上的组件高达数亿至数十亿个。

早期,半导体公司多是从IC设计、制造、封装、测试到销售都一手包办的整合组件制造商(Integrated Device Manufacturer, 俗称IDM),如英特尔 (Intel)、德州仪器 (TI)、摩托罗拉(Motorola)、三星 (Samsung)、菲利普 (Philips)、东芝 (Toshiba),以及国内的华邦、旺宏。

然而,由于摩尔定律的关系,半导体芯片的设计和制作越来越复杂、花费越来越高,单独一家半导体公司往往无法负担从上游到下游的高额研发与制作费用,因此到了1980年代末期,半导体产业逐渐走向专业分工的模式──有些公司专门设计、再交由其他公司做晶圆代工和封装测试。

1987年台积电 (TSMC) 成立。

由于一家公司只做设计、制程交给其他公司,容易令人担心机密外泄的问题 (比如若高通和联发科两家彼此竞争的IC设计厂商若同时请台积电晶圆代工,等于台积电知道了两家的秘密),故一开始台积电并不被市场看好。

然而,台积电本身没有出售芯片、纯粹做晶圆代工,更能替各家芯片商设立特殊的生产线,并严格保有客户隐私,成功证明了专做晶圆代工是有利可图的。

如今台积电是全球排名第一的晶圆代工公司。知名厂商亦包括全球排名第二的联电 (UMC)、格罗方德 (GlobalFoundries)、中芯 (SMIC)。

由于IC设计公司只设计和销售芯片,但将制造、封装、测试外包给第三方、以专心投入资金与人力研发,故被称为无厂半导体 (Fabless Semiconductor Company),包括高通 (Qualcomm)、博通 (Broadcom)、联发科 (MediaTek),与中国紫光集团下的展讯 (SpreadTrum)。

最后,台湾半导体封装大厂日月光(ASE)排名全世界第一,全球市占近20%。排名第二为美商艾克尔(Amkor)、第三亦为台湾厂商硅品(SPIL)。

半导体产业在近数十年来的发展速度不只惊人,许多重大的创新也支持了众多其他产业也、产生了极大的影响,可以说是数字时代之母。毫无疑问地,在未来,半导体的应用与产业规模,将会比今日来的更加广泛且举足轻重。

补充:

电路设计图是 IC 设计厂在看的,晶圆代工厂拿到的会是经转换过的线路Layout设计图,也就是Layout GDS檔。.gds 文件格式的扩展名的意思是与Chip Layout Information相关的模拟CAD档案。(CAD指用计算机软件仿真实物设计)

电路设计图转换成Layout图时,会根据各家代工厂的Design Rule而有所不同。各家代工厂的 Design Rule 是和该代工厂自家的制程能力与制程方式而有所差异。

微影成像完后,严格上来说图形是还没转换到晶圆上的,此时只是把图形转换到光阻上(就是内文比喻的底片),之后经过干蚀刻往下挖挖挖,才会把图形转印到晶圆上。